用于构建基于FPGA系统的Python SoC/核心构建器。

项目描述

Copyright 2012-2023 / Enjoy-Digital & LiteX developers

欢迎使用LiteX!

LiteX框架提供了一个方便且高效的架构,用于创建FPGA Core/SoC,探索各种数字设计架构,并创建基于FPGA的完整系统。

LiteX SoC构建器框架快速游览/概述: 幻灯片

想要开始并/或寻找文档?请确保访问Wiki!

有问题或想要联系?加入我们吧,在Discord或我们的IRC频道:[#litex at irc.libera.chat].

LiteX提供了创建FPGA Core/SoC所需的全部常见组件

- :heavy_check_mark: 总线和流(Wishbone、AXI、Avalon-ST)及其互连。

- :heavy_check_mark: 简单核心:RAM、ROM、定时器、UART、JTAG等...

- :heavy_check_mark: 通过核心生态系统创建复杂核心:LiteDRAM、LitePCIe、LiteEth、LiteSATA等...

- :heavy_check_mark: 各种CPU & ISAs:RISC-V、OpenRISC、LM32、Zynq、X86(通过PCIe)等...

- :heavy_check_mark: 支持多种语言与VHDL/Verilog/(n)Migen/Spinal-HDL等...集成。

- :heavy_check_mark: 通过各种桥接器和Litescope,提供了强大的调试基础设施。

- :heavy_check_mark: 通过Verilator进行直接/快速仿真。

- :heavy_check_mark: 为开源和供应商的工具链构建后端。

- :heavy_check_mark: 以及更多... :)

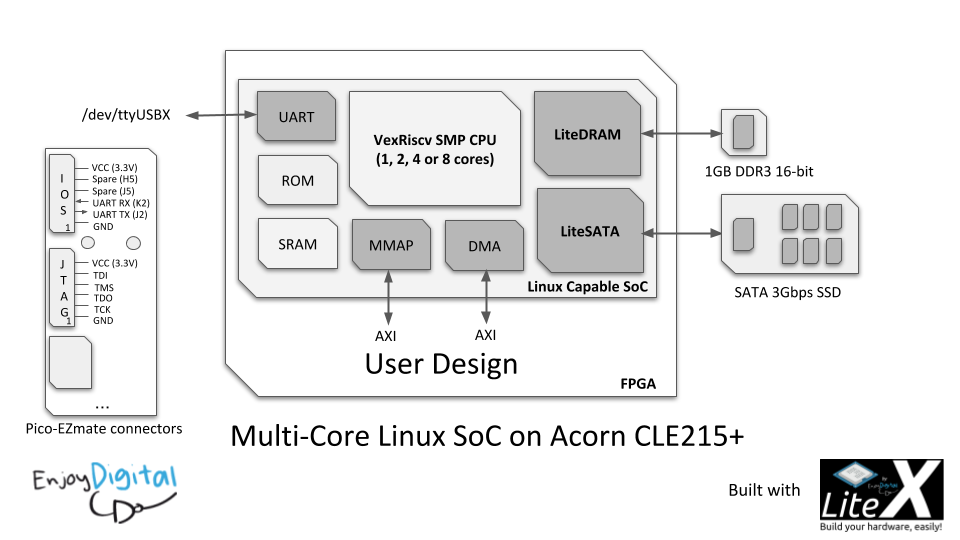

通过将LiteX与核心生态系统相结合,与传统的做法相比,创建复杂的SoC变得容易得多,同时提供更好的可移植性和灵活性:例如,这是一个基于VexRiscv-SMP CPU、LiteDRAM、LiteSATA的、由LiteX构建和集成的多核Linux Capable SoC,运行在廉价的Acorn CLE215+ Mining Board上:

目前,LiteX的数字逻辑使用Migen进行描述,这并不阻止用户创建混合语言项目。

- 在LiteX中集成VHDL/Verilog/SystemVerilog/nMigen/Spinal-HDL代码非常普遍且简单。

- 也很常见,反过来将LiteX设计作为verilog文件生成,并将其集成到传统的流程中。

LiteX最初由Enjoy-Digital开发,用于为客户创建项目(并且我们仍在为此目的使用它 :))。考虑到不同客户的需求/需求,我们认为该框架非常灵活。

- 一些用户只想用它轻松连接他们现有的VHDL/Verilog/SV核心。

- 一些用户只对重新使用PCIe/Ethernet/SATA等核心作为常规核心,并将其集成到他们的传统流程中感兴趣。

- 一些具有硬件背景的用户从上述方法开始,然后稍后切换到完整的Python流程,因为觉得它更有效。

- 一些具有软件背景并且精通Python的用户在接触FPGA时开始玩,否则他们可能永远不会接触FPGA :)

- 等等...

我们深知每个人都有不同的背景,所以选择适合您的LiteX方法由您自己决定!

要开始,我们鼓励您阅读wiki。

您已经有了FPGA板吗?访问LiteX-Boards查看您的板是否已受支持!

该框架也远非完美,我们很乐意接受您的反馈或/和贡献。

祝您玩得开心! :wink

道德上的精确性:该项目以BSD 2-Clause许可证共享,我们鼓励继续以这种方式共享,多亏了出色的社区和愿意支持项目的客户!如果该项目对您的研究、爱好或商业项目有用,我们只是要求您保持一致并行为端正:不要期待免费支持或社区会欢迎那些在项目上抱怨(然后不尊重开发者)或未支付您要求的定制开发的人...(虽然这可能对99%的用户/客户来说是自然的,但似乎有必要为剩余的1%添加这一点,他们消耗了我们大量的精力和时间)。

典型的LiteX设计流程

+---------------+

|FPGA toolchains|

+----^-----+----+

| |

+--+-----v--+

+-------+ | |

| Migen +--------> |

+-------+ | | Your design

| LiteX +---> ready to be used!

| |

+----------------------+ | |

|LiteX Cores Ecosystem +--> |

+----------------------+ +-^-------^-+

(Eth, SATA, DRAM, USB, | |

PCIe, Video, etc...) + +

board target

file file

LiteX已支持各种软核CPU:VexRiscv、Rocket、LM32、Mor1kx、PicoRV32、BlackParrot,并且与LiteX的核生态系统兼容

| 名称 | 构建状态 | 描述 |

|---|---|---|

| LiteX-Boards |  |

板支持 |

| LiteDRAM |  |

DRAM |

| LiteEth |  |

以太网 |

| LitePCIe |  |

PCIe |

| LiteSATA |  |

SATA |

| LiteSDCard |  |

SD卡 |

| LiteICLink |  |

片间通信 |

| LiteJESD204B |  |

JESD204B |

| LiteSPI |  |

SPI/SPI-Flash |

| LiteScope |  |

逻辑分析仪 |

使用LiteX构建的设计示例

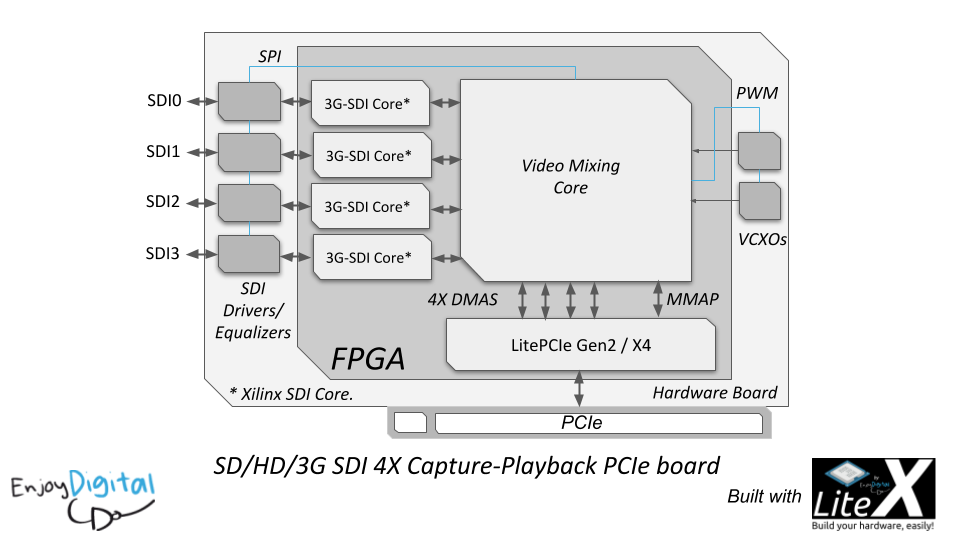

基于LitePCIe和集成LiteX的自定义PCIe SDI捕获/回放板,允许完全控制SDI流和极低延迟。

要发现更多使用LiteX构建的产品/项目,请访问Wiki上的项目页面。

赞助商/合作伙伴

向我们的出色工业客户提供大力支持,他们允许我们将最初为他们创建的一些发展直接集成到LiteX中!这些创新的发展往往为更广泛社区使用的功能提供构建块。您的支持对该项目至关重要,我们非常感谢您的合作。谢谢!

论文、演讲、教程、链接

FPGA课程/教程

Migen教程

OSDA 2019论文/幻灯片

LiteX-Vexriscv上的Linux

RISC-V入门指南

LiteX与Vivado第一印象

35C3 - 蛇和兔子 - 如何CCC塑造了一个开源硬件的成功

Tim的项目太多 - LatchUp版本: https://www.youtube.com/watch?v=v7WrTmexod0

子包

litex.gen提供特定或实验性模块,用于生成Migen中未集成的HDL。

litex.build提供构建FPGA位流(接口到供应商工具链)和模拟HDL代码或全SoC的工具。

litex.soc提供构建核心(总线、存储器、流)的定义/模块,以及构建SoC的核心和工具。

快速入门指南

- 安装Python 3.6+和FPGA供应商的开发工具和/或Verilator。

- 安装Migen/LiteX以及LiteX的核心

$ wget https://raw.githubusercontent.com/enjoy-digital/litex/master/litex_setup.py

$ chmod +x litex_setup.py

$ ./litex_setup.py --init --install --user (--user to install to user directory) --config=(minimal, standard, full)

稍后,如果您需要更新所有存储库

$ ./litex_setup.py --update

注意:在MacOS上,请确保您已安装HomeBrew。然后执行,

brew install wget。

注意:在Windows上,您可能需要将

SHELL环境变量设置为SHELL=cmd.exe。

- 安装RISC-V工具链(如果您想测试/创建带有CPU的SoC)

$ pip3 install meson ninja

$ ./litex_setup.py --gcc=riscv

- 构建您的板卡的目标...

转到litex-boards/litex_boards/targets并执行您想要构建的目标。

- ...以及/或者安装Verilator,直接在您的计算机上测试LiteX,无需任何FPGA板

在Linux (Ubuntu)

$ sudo apt install libevent-dev libjson-c-dev verilator

$ litex_sim --cpu-type=vexriscv

在MacOS

$ brew install json-c verilator libevent

$ brew cask install tuntap

$ litex_sim --cpu-type=vexriscv

- 在115200 8-N-1下运行板卡的串行端口终端程序。

您应该会得到以下BIOS提示。

社区

多年来,围绕LiteX和核心生态系统已经形成了一个友好的社区。反馈和贡献已经极大地提升了项目,EnjoyDigital仍然领导着开发,但现在它是一个社区项目,围绕/与LiteX创建的协作项目可以在https://github.com/litex-hub找到。

联系方式

项目详情

litex-2023.12.tar.gz的哈希值

| 算法 | 哈希摘要 | |

|---|---|---|

| SHA256 | 4710694f5271990d2fde0c6d7b6989ec1ad72ccbab4161adeb5d6be51d6e36d4 |

|

| MD5 | 745a43b189d46f2ffb5c0be2efe99385 |

|

| BLAKE2b-256 | 4b4ce44af592ea8085f894a80f79f46761e9dc44ab0d79ef3f06ecbd83b4d240 |