小体积且可配置的SATA核心

项目描述

__ _ __ _______ _________

/ / (_) /____ / __/ _ /_ __/ _ |

/ /__/ / __/ -_)\ \/ __ |/ / / __ |

/____/_/\__/\__/___/_/ |_/_/ /_/ |_|

Copyright 2014-2022 / EnjoyDigital

Copyright 2014-2015 / HKU

A small footprint and configurable SATA core

powered by Migen & LiteX

[> 简介

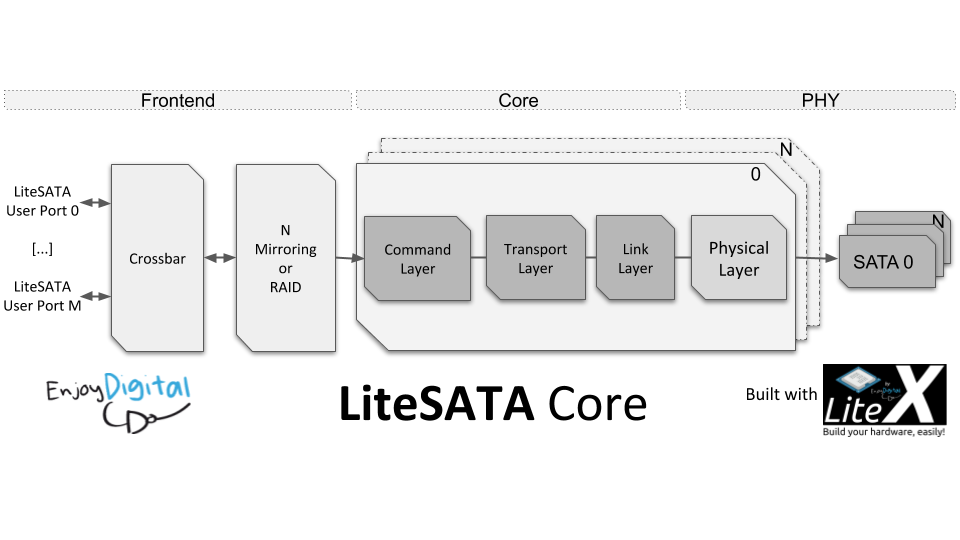

LiteSATA提供小体积和可配置的SATA核心。

LiteSATA是LiteX库的一部分,其目的是通过提供简单、优雅且高效的组件实现来降低复杂FPGA核心的入门门槛,这些组件用于今天的SoC,如以太网、SATA、PCIe、SDRAM控制器等。

使用Migen描述HDL可以使核心高度且易于配置。

LiteSATA可以作为LiteX库使用,也可以通过生成您将用作标准核心的Verilog RTL来与您的标准设计流程集成。

[> 特性

PHY

- Xilinx 7系列(Kintex7,Artix7)

- Xilinx Ultrascale(+)系列

- OOB、COMWAKE、COMINIT

- K28.5上的ALIGN插入器/移除器和字节对齐

- 收发器中的8B/10B编码/解码

- 自动TX/RX P/N极性检测和交换。

- 错误检测和报告

- 32位接口

- 支持1.5/3.0/6.0GBps的速度(分别对应37.5/75/150MHz的系统时钟)

核心

- 链路

- CONT插入器/移除器

- 数据的加扰/去扰

- CRC插入器/检查器

- HOLD插入/检测

- 错误检测和报告

- 传输/命令

- 易于使用的用户界面(可以与或没有CPU一起使用)

- 48位扇区寻址

- 支持3个命令:READ_DMA(_EXT)、WRITE_DMA(_EXT)、IDENTIFY_DEVICE

- 错误检测和报告

前端

- 可配置的交叉开关(只需声明您的交叉开关,然后使用crossbar.get_port()添加新端口!)

- 端口仲裁对用户透明

- 可综合的BIST

- 条带模块,用于在多个硬盘上分割数据,提高读写速度和容量。(RAID0等效)

- 镜像模块,用于数据冗余和提高读取速度。(RAID1等效)

[> FPGA验证

LiteSATA已被用于商业和开源设计

- 高分辨率50M像素CMOS相机使用CFAST和SD卡。

- 低延迟数据库研究。

[> 可能的改进

- 添加标准化接口(AXI、Avalon-ST)

- 添加NCQ支持

- 添加AES硬件加密

- 添加流式压缩/解压缩功能

- 添加对Altera PHY的支持。

- 添加对Lattice PHY的支持。

- 添加Zynq Linux驱动程序。

- ... 请参阅下面的支持和咨询 :)

如果您想支持这些功能,请联系我们 florent [AT] enjoy-digital.fr。

[> 入门指南

- 安装Python 3.6+和FPGA厂商的开发工具。

- 按照LiteX的wiki 安装指南 安装LiteX和核心。

- 您可以在LiteX-Boards和示例目录中找到核心与LiteX集成的示例。

[> 测试

单元测试位于 ./test/。要运行所有单元测试

$ ./setup.py test

也可以单独运行测试

$ python3 -m unittest test.test_name

[> 许可证

LiteSATA在非常宽松的两条款BSD许可证下发布。根据本许可证条款,您有权将LiteSATA用于封闭源代码的专有设计。尽管我们不要求您这样做,但这些事情很棒,因此如果可能,请这样做

- 告诉我们您正在使用LiteSATA

- 在其研究相关的出版物中引用LiteSATA

- 向我们发送反馈和建议改进

- 当出现问题时报错

- 将您对LiteSATA所做的修改和改进发送给我们。

[> 支持和咨询

我们热爱开源硬件,喜欢与他人分享我们的设计。

LiteSATA由EnjoyDigital开发和维护。

如果您想了解更多关于LiteSATA的信息,或者您已经是快乐的用户并希望将其扩展到您的需求,EnjoyDigital可以提供标准商业支持和咨询服务。

因此,请随时联系我们,我们很乐意与您合作!(并最终缩短可能改进的列表 :)

[> 联系方式

电子邮件:florent [AT] enjoy-digital.fr

项目详情

关闭

litesata-2023.12.tar.gz的哈希值

| 算法 | 哈希摘要 | |

|---|---|---|

| SHA256 | 93cf15665b4e72a50e267034f31cc829ecfd6bb30aa08c84ed8c94df99d6e077 |

|

| MD5 | 2c3409c38368fb198682b2789ba7d022 |

|

| BLAKE2b-256 | 57b0dabf1bb0a143c8a444c0de84d015629309879f39448a4444fc3d3944d8df |